トップページ > APIC21

ご注意

APIC21はPCI2.3以前の5Vシステム環境(V(I/O)=5V)でのみ動作いたします。

PCI3.0やPCI2.3以前の3.3Vシステム環境(V(I/O)=3.3V)の場合はAPIC22をご使用ください。

概要

|

含有物質についてはこちら

APIC21の含有物質については、chemSHERPAの形式にてご用意できます。 詳しくはこちらからお問い合わせください。

詳細技術資料はこちら

APIC21技術資料PDFファイルダウンロード(1401KB) 第4版

APIC21取扱について

APIC21取扱についてPDFファイルダウンロード(197KB)

APIC21に関する具体的な疑問にお答えするFAQです。

PCIバスとの接続方法など役に立つ情報も掲載されています。ぜひご覧ください。 APIC21 テクニカルサポート Q&A

APIC21開発キット APIC21DK (販売中止)

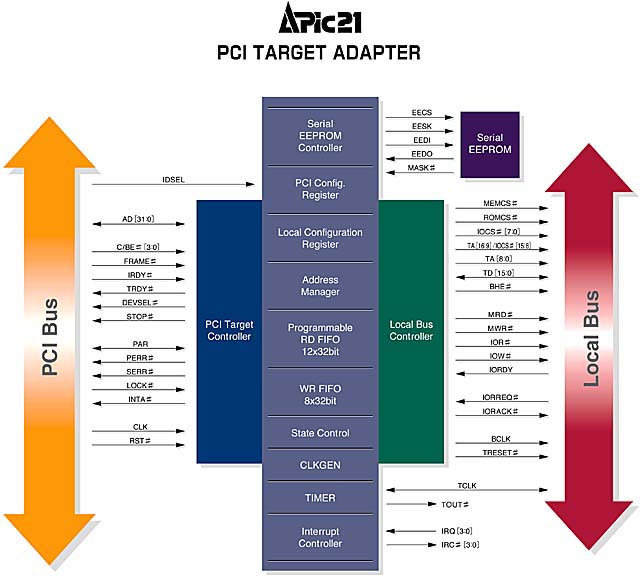

PCIターゲットインターフェースアダプタ『APIC21』の性能と手軽さを試していただくため、 『APIC21』を中心として必要なものをパッケージングしたものが、『APIC21DK』PCIバスボード開発キット・ 「APIC21DK/CPCI」CompactPCIバスボード開発キットです。 APIC21開発キットについてはこちらのページへ

APIC22(PCIバスインターフェースアダプタ)

PCI Local Bus 規格2.2マスタ/ターゲット機能に準拠し、ローカルバス幅32bit/3.3V/マスタ転送/ホットスワップに対応したAPIC22を 用意しています。APIC22についてはこちらのページへ